芯片资讯

你的位置:CMOS图像传感器IC集成电路芯片-亿配芯城 > 芯片资讯 > FPGA图像处理_ISP算法DPC流程

FPGA图像处理_ISP算法DPC流程

- 发布日期:2023-12-26 13:50 点击次数:209

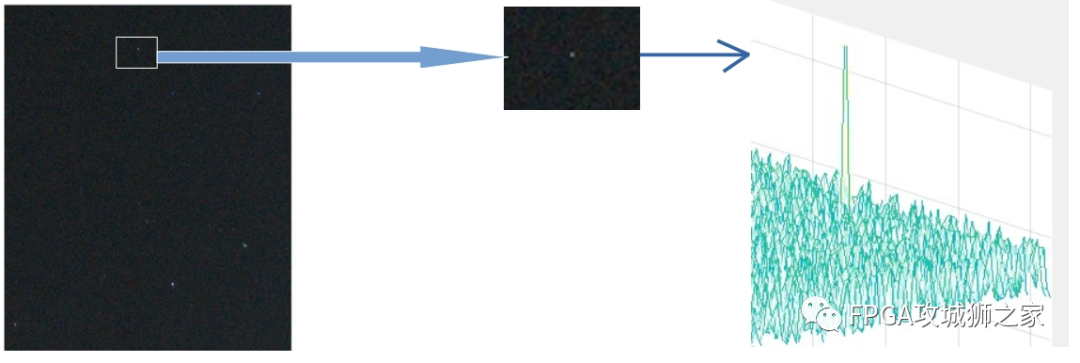

DPC通常作为ISP算法流程里面的第一个模块,原理也很简单。DPC 应对的主要问题是传感器像素的缺陷,这些缺陷可能源于制造缺陷、长期磨损或外部因素如灰尘侵入,这些缺陷像素在成像时无法准确记录光线信息,表现为静态的亮点、暗点或彩点,从而破坏图像的整体质量

坏点校正技术的实施通常涉及两个阶段:检测和校正。在检测阶段,算法分析传感器输出的原始图像数据,识别出异常。 然后,在校正阶段,利用周围正常像素的值采用插值等方法对这些异常像素进行修复。 这一过程的关键在于恰当平衡,以去除缺陷的同时尽可能保留图像的真实细节。 当 DPC 算法得当,EEPROM带电可擦可编程存储器芯片大全其结果是让最终图像在视觉上免受这些缺陷像素的影响, 芯片交易网IC交易网保证了图像质量的准确性和一致性。

运算的一般方法为 1, ATMEGA系列ATMEL芯片COM在邻域的 3*3 区域内, CMOS图像传感器集成电路芯片对比中心像素与周围像素之间的差值, 电子元器件PDF资料大全如此得到 8 个差值 2,CMOS图像传感器IC集成电路芯片如果第一步中得到的 8 个差值同为正数,或者同为负数,并且所有值的绝对值大于设定的阈值,那么进行第三步。否则直接输出原有的中心像素值。 3,在 3 * 3 的区域内,找到中值。 4,用中值替换掉原来的中心像素值

上述模块的精彩之处在于: 1,LineBuffer 进行了IP 化,可以任意多行并行输出。 2,中值滤波本来可以很简单,但是本文中采用方法独特,时序最优,占用资源最少。 3,代码从400M的主频跑到了600M,优化之后跑到了725M 的主频。 4,讲解如何进行时序优化

审核编辑:刘清

相关资讯

- 全球FPGA芯片市场布局2025-10-08

- Cyclone系列FPGA:高性能可编程逻辑解决方案的技术解析与应用场景2025-08-25

- FPGA实现ISP常见2D去噪的方法2024-01-05

- FPGA加速语言模型如何重塑生成式人工智能2024-01-05

- 全球最大的FPGA——VP19022024-01-05

- 如何在FPGA上快速搭建以太网?2024-01-05